TEMPORIZADOR DIGITAL

TEMPORIZADOR DIGITAL PROGRAMABLE

FASE 2: CIRCUITOS CONTADORES CON FLIP FLOPS

1.-CAPACIDAD TERMINAL:

- Identificar las aplicaciones de la Electrónica Digital.

- Describir el funcionamiento de las unidades y dispositivos de almacenamiento de información.

- Implementar circuitos de lógica combinacional y secuencial.

2.-COMPETENCIA ESPECÍFICA DE LA SESIÓN:

- Implementación de circuitos mono-estables.

- Implementación con circuitos contadores con FLIP FLOPS JK.

- Utilizar un simulador para comprobar el funcionamiento de los mismos.

3.-CONTENIDOS A TRATAR:

- Circuitos Mono-estables.

- Circuitos de contadores ascendentes y descendentes.

- Aplicaciones con circuitos contadores.

4.-MARCO TEÓRICO:

Hay dos tipos de elementos de memoria basados en el tipo de activación que es adecuado para operarlo.

- - Latches

- - Flip Flop's

Los latches funcionan con señal de habilitación, que es sensible al nivel . Mientras que, los flip-flops son sensibles al borde. Tipos de latches:

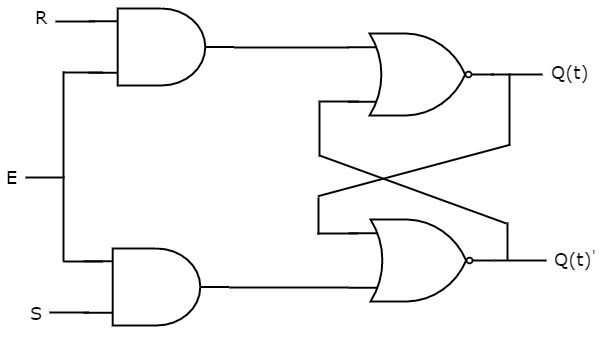

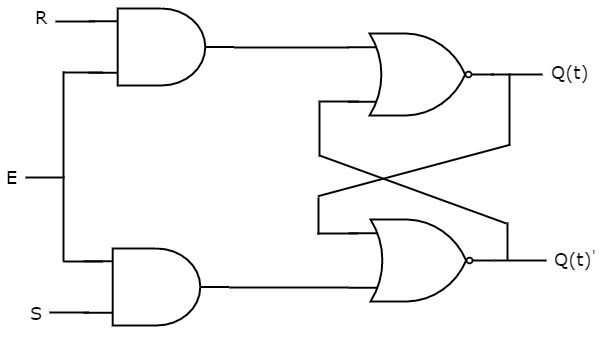

SR LATCH:

SR Latch también se denomina Establecer restablecer pestillo . Este pestillo afecta a las salidas siempre que la habilitación, E se mantenga en '1'. El diagrama de circuito de SR Latch se muestra en la siguiente figura.

Este circuito tiene dos entradas S & R y dos salidas Q (t) y Q (t) '. La puerta NOR superior tiene dos entradas R y complemento del estado presente, Q (t) 'y produce el siguiente estado, Q (t + 1) cuando está habilitado, E es' 1 '.

De manera similar, la puerta NOR inferior tiene dos entradas S & estado presente, Q (t) y produce el complemento del siguiente estado, Q (t + 1) 'cuando está habilitado, E es' 1 '.

Sabemos que una puerta NOR de 2 entradas produce una salida, que es el complemento de otra entrada cuando una de las entradas es '0'. Del mismo modo, produce salida '0', cuando una de las entradas es '1'.

- Si S = 1, entonces el siguiente estado Q (t + 1) será igual a '1' independientemente del estado actual, valores Q (t).

- Si R = 1, entonces el siguiente estado Q (t + 1) será igual a '0' independientemente del estado actual, valores Q (t).

En cualquier momento, solo de esas dos entradas debe ser '1'. Si ambas entradas son '1', entonces el siguiente estado Q (t + 1) no está definido.

La siguiente tabla muestra la tabla de estado del bloqueo de SR.

| S | R | Q (t + 1) |

|---|---|---|

| 0 | 0 | Q (t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | - |

Por lo tanto, SR Latch realiza tres tipos de funciones, como Hold, Set & Reset en función de las condiciones de entrada.

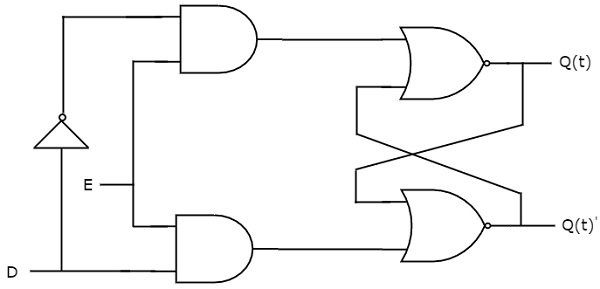

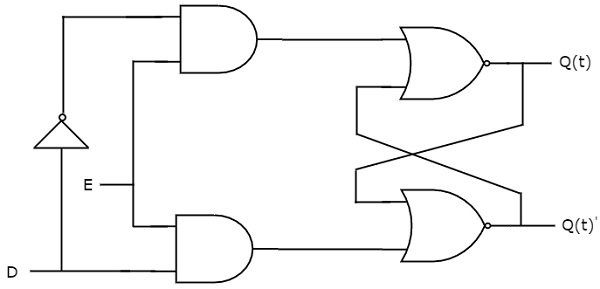

D LATCH:

Hay un inconveniente de SR Latch. Ese es el siguiente valor de estado que no puede predecirse cuando las dos entradas S & R son una. Entonces, podemos superar esta dificultad con D Latch. También se llama como Data Latch. El diagrama de circuito de D Latch se muestra en la siguiente figura.

Este circuito tiene una entrada única D y dos salidas Q (t) y Q (t) '. D Latch se obtiene de SR Latch colocando un inversor entre las entradas S amp; y R, y conectando la entrada D a S. Eso significa que eliminamos las combinaciones de S & R que son del mismo valor.

- Si D = 0 → S = 0 & R = 1, el siguiente estado Q (t + 1) será igual a '0' independientemente del estado presente, valores Q (t). Esto corresponde a la segunda fila de la tabla de estado de SR Latch.

- Si D = 1 → S = 1 & R = 0, el próximo estado Q (t + 1) será igual a '1', independientemente del estado actual, valores Q (t). Esto corresponde a la tercera fila de la tabla de estado SR Latch.

La siguiente tabla muestra la tabla de estado de P latch.

| re | Q (t + 1) |

|---|---|

| 0 | 0 |

| 1 | 1 |

Por lo tanto, D Latch Mantiene la información que está disponible en la entrada de datos, D. Eso significa que la salida de D Latch es sensible a los cambios en la entrada, D siempre que la habilitación sea High.

En este capítulo, implementamos varios cierres proporcionando el acoplamiento cruzado entre puertas NOR. Del mismo modo, puede implementar estos cierres utilizando puertas NAND.

Entradas SET y CLEAR – Flip Flop JK

Existen dos entradas adicionales en el biestable o flip flop JK muy importantes:

– La entrada PRESET (poner), que sirve para poner directamente en el biestable un “1” en la salida Q

– La entrada CLEAR (borrar), que sirve para poner en “0” en la salida Q.

Estas entradas son asincrónicas, lo que significa que tendrán efecto sin importar el estado del reloj y/o las entradas J y K. Es importante no activar simultáneamente estas dos entradas. Importante: Los biestable pueden “TENER o NO TENER” una pequeña burbuja (esfera, bolita) en las entradas PRESET o CLEAR.

– Cuando NO la tienen significa que la señal es activa cuando está en nivel ALTO.

– Cuando SI la tienen significa que la señal es activa cuando está en nivel BAJO.

El diagrama completo del biestable JK será como se muestra en el diagrama anterior.

*Tabla de verdad del Flip Flop JK

De la tabla de verdad anterior se puede ver que las entradas CLEAR (CLR) y PRESET son activas en bajo (ver la pequeña esfera en estas entradas) y se imponen en la salida Q sin importar el estado del reloj y de las entradas J y K. (ver las entradas J, K y el reloj con una X). Para que las entradas J y K y el reloj sean funcionales, las entradas Clear y Preset deben de estar en nivel “alto” (no activas), entonces:

- Memorizar: Con J = 0 y K = 0, hay un estado de memoria o retención (mantiene la salida que tenía antes de que las entradas hayan cambiado).

- Reset: Con J = 0 y K = 1, se pode en Q un “0” y Q en un “1”.

- Set: Con J = 1 y K = 0, se pode en Q un “1” y en Q un “0”.

- Bascular: Con J = 1 y K = 1, el biestable bascula pasando de un nivel a otro (“0” a “1” o “1” a “0”).

Lo anterior sólo tiene efecto en el momento en que el pulso de reloj está en el flanco descendente o posterior (ver la flecha en la columna “Reloj”)

Notas:

- bascular = cambiar de estado. Si estaba en “1” pasa a “0” y al revés

- FF = biestable

- síncronas = sincrónicas

- asíncronas = asincrónicas

5.-DESARROLLO DE ACTIVIDADES:

5.1.-DETERMINE LA ECUACIÓN LÓGICA Y TABLA DE VERDAD DEL CIRCUITO:

Ecuación: R*q+S= Q

5.2.- SIMULANDO EL COMPORTAMIENTO DE LOS CIRCUITOS:

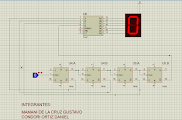

5.3.- ARMADO DE CIRCUITO CON FLIP FLOP´S:

5.4 SOLUCIÓN DE RETO:

6.- VIDEO DEMOSTRATIVO (OBSERVE LOS SIGUIENTES ENLACES):

7.- OBSERVACIONES Y CONCLUSIONES:

* OBSERVACIONES:

Se observó, que para lograr que el contador en el circuito solo llegue a nueve se requirió de la compuerta NAND (7400 o 7403) la cual al cumplir con su función ya estudiada anteriormente realizó que se vuelva a iniciar desde cero.

Para lograr el reto solo se cambio la posición de salida de Q a (Q´ = negado), manteniendo lo demás tal como y sus respectivas conexiones al integrado 7447.

* CONCLUSIONES:

Se concluye que se pudo implementar circuitos de lógica combinacional y secuencial según lo desarrollado en el laboratorio.

Se concluye que se logro de la identificación de las aplicaciones de la electrónica digital tales como los integrados usados (7473, decodificador 7447, etc).

8.- BIBLIOGRAFÍA:

·

Floyd, Thomas (2006) Fundamentos de sistemas

digitales. Madrid.: Pearson Educación

(621.381/F59/2006) Disponible Base de Datos Pearson

·

Mandado, Enrique (1996) Sistemas electrónicos

digitales. México D.F.: Alfaomega.

(621.381D/M22/1996)

·

Morris Mano, M. (1986) Lógica digital y diseño de

computadoras. México D.F.: Prentice Hall (621.381D/M86L)

·

Tocci, Ronald (2007) Sistemas digitales: Principios y

aplicaciones. México D.F.: Pearson

Educación. (621.381D/T65/2007) Disponible Base de Datos Pearson

INTEGRANTES:

- Condori Ortiz Daniel Agustín

- Mamani de La Cruz Gustavo

Comentarios

Publicar un comentario